# Mehran University Research Journal of Engineering and Technology

https://doi.org/10.22581/muet1982.2303.11

2023, 42(3) 102-109

# Computationally efficient low-power sigma delta modulation-based image processing algorithm

Aneela Pathan<sup>a</sup>, Tayab D Memon<sup>b</sup>, Saleem Raza<sup>c</sup>, Rizwan Aziz Mangi<sup>a</sup>

<sup>a</sup> Department of Electronic Engineering, Quaid-e-Awam University of Engineering, Science, and Technology Campus Larkana Pakistan

<sup>b</sup> Department of Electronic Engineering, Mehran University of Engineering and Technology, Jamshoro Pakistan

<sup>c</sup> Centre for Artificial Intelligence Research & Optimization Design and Creative Technology Vertical, Torrens University, Melbourne Australia

\* Corresponding author: Aneela Pathan, Email: pathan aneela@quest.edu.pk

Received: 17 February 2023, Accepted: 26 June 2023, Published: 01 July 2023

#### **KEYWORDS** ABSTRACT Sigma-Delta Modulation Digital Image Processing has dominated Digital Signal Processing at the cost of more memory, resources, and high computational power. In image processing, **Image Processing** filtering transformations and other operations need complex multiplications, and Low-Power the multiplier is one of the most resources consuming elements. Recently, mitigating the multiplier complexity in the digital signal processing (DSP) Power-Efficient algorithms sigma-delta modulation based general purpose and adaptive DSP Artificial Intelligence algorithms are developed in MATLAB and compared with its counterpart multibit algorithms for functionality and area-performance-power in FPGA. The contemporary multiplier algorithms are also optimized to overcome the multiplier complexity challenge as computation becomes simple and fast. This paper extends the reported work by investigating the sigma-delta modulation approaches for developing a computationally efficient low-power image processing algorithm. The proposed model is designed, developed, and simulated in MATLAB. The simulation results are analyzed using SNR, MSE, and Peak SNR. The simulation results show that the proposed system can better mitigate the noise effect, making it robust for noisy environment.

# 1. Introduction

Image processing has various applications in diversified science fields [1-3]. The images are often captured, processed, stored, and transmitted [4]. The image takes sufficient memory, substantial computational resources, and power [5, 6].

In image processing, filtering transformations and other operations need complex multiplications, and the multiplier is one of the most resources consuming

© Mehran University of Engineering and Technology 2023

elements [7, 8]. The research proposes various traditional and nontraditional multiplier optimization methods and schemes and implements software based or on hardware (ASICS and FPGAs) [9-13].

As image transmission requires high bandwidth and energy, the telecommunication companies must minimize the bandwidth and energy footprint of media transmissions and reduce the ever-increasing traffic load due to multimedia traffic [14]. The traditional method to reduce the bandwidth is compression, which is also reported in recent literature [15-17]. The main goal of the compression technique is to eliminate the redundancy of image data so that the digital image will be stored and transmitted more effectively.

Semantic communication has also gained the attention of industries and researchers as it permits to go beyond Shannon's capacity limit in bandwidth-limited communication channels. The objective is to deliver the semantic meaning of the message and not the exact form of the message by sharing a common, prior knowledge and a semantically encoded message, which is expected to perform better than state-of-the-art compression techniques, thereby drastically reducing the physical bandwidth requirement between the transmitter and receiver [18-21].

In image transmission, systems adopt separate channel coding and source coding, where the length of the codeword needs to be (infinitely) long [22]. Thus, using joint source-channel coding (JSCC) can enable significant gains. Joint source-channel coding is the encoding of a redundant information source for transmission over a noisy channel and the corresponding decoding, using a single code instead of the more conventional steps of source coding followed by channel coding. Deep learning has also been extended to JSCC systems for wireless image transmission to perform better than separated source and channel coding [17, 23-25].

Though the deep learning approaches may achieve substantially better accuracy; however this jump comes at the cost of billions of additional math operations and an increased requirement for processing power. In this case, the SDM-based short-word-length image processing algorithms can reduce the overall processing of deep learning models and give better results regarding computation time, processing power, and floor chip area requirements [26].

Generally, SDM, like PCM, was initially introduced for analog to digital conversion [27], but since the '70s, it has diversified its application domain toward data length reduction. The SDM converts the multi-bit data into single-bit (stream of bits); hence, the single-bit data is processed. The benefits of SDM include but are not limited to low cost due to less complicated implementation and no digital multipliers, which results in reduced chip area requirement and low computational power. Some of the SDM-based DSP systems include FIR filters [28], IIR filters [29], Matched filters [30], Digital Arithmetic Units [31], Adaptive filters [32-35], and Smart Sensor Communications [36].

Recent research demonstrates that the SDM reduces the word length and improves the system's overall quality [37].

To the best of our knowledge, the applications of SDM are still prominent in single-dimensional voice or data signals; its use in multi-dimensional images has yet to be investigated.

This paper proposes an SDM-based architecture of multi-dimensional image processing. It investigates the transmission of SDM-based images in a noisy environment to validate the acceptance of SDM in the new digital image processing domain.

The proposed system is designed, developed, and simulated in MATLAB, which may be carried out for hardware synthesis and its functional verification on a suitable platform like FPGA. The simulation results are further evaluated based on performance parameters, including signal-to-noise ratio (SNR), means squared error (MSE), and Peak SNR. The simulation results show that the proposed sigma-delta modulation-based image processing system offers comparable results and observes less effect of noise. This result makes the proposed design very suitable for noisy environment.

The rest of the paper proceeds as follows. An introduction to sigma-delta modulation is given in section 2, followed by the proposed single-bit SDM-based image processing and transmission system in section 3. In section 4, the proposed design is simulated, and the results are compared with the contemporary multi-bit image transmission system. Section 5 concludes the paper, followed by the point to the future work.

# 2. Sigma-Delta Modulation ( $\Sigma$ - $\Delta$ ADC)

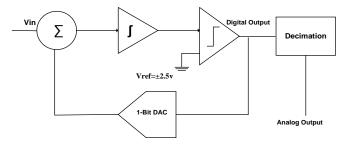

The analog to digital converters can be divided into two categories depending on the sampling ratio. The first category is the Nyquist rate ADCs, in which the input data is sampled at the Nyquist rate, and the second type, an oversampling ADCs, samples the signal at a rate much higher than the Nyquist rate. Sigma-delta modulators (Fig.1) come under the over-sampling converters (by oversampling, the sampling frequency is increased by a factor, k, and the noise energy is distributed over a broader range of frequencies) [38]. The transmission efficiency of SDM based system is higher, as instead of sending full data values, only the changes (delta) in value between consecutive samples are transmitted.

Fig. 1. Sigma-delta modulator

The Sigma-delta modulator design of Fig. 1 consists of a summing node, an integrator, a comparator, and a D/A converter. The first block is the difference block (summing note) to which analogue input is applied, and from it, the feedback signal (DAC output) is subtracted. The proceeding block is the integrator that stores the difference. The comparator block works on the output of the integrator where the reference signal is already available. The reference voltage levels are compared with the integrator's output, generating a "high" or "low" value. In turn, the DAC uses the result of the ADC and develops one of the two available reference voltages. This reference voltage is passed to the difference block to be subtracted from the input again. Moreover, in the last, one-bit (high/low) data samples are decimated (down-sampled) by the digital filter to achieve the same data rate when reconverted into an analog.

The output voltage at various blocks of sigma-delta ADC is given in Table 1 for one-volt analog input and 2.5 volts as a reference voltage.

#### Table 1

| Output voltage |                                    |                   |                 |      |

|----------------|------------------------------------|-------------------|-----------------|------|

| Vin<br>=1      | Difference block<br>(Summing Node) | Integrator output | Comp-<br>arator | DAC  |

|                | 1                                  | 1                 | Н               | 2.5  |

|                | 1-(2.5)=1.5                        | 1+(-1.5)=0.5      | L               | -2.5 |

|                | 1-(-2.5)=3.5                       | (-0.5+3.5)=3      | Н               | 2.5  |

|                | 1-(2.5)=1.5                        | 3+(-1.5)=1.5      | Н               | 2.5  |

|                | 1-(2.5)=1.5                        | 1.5+(-1.5)=0      | Н               | 2.5  |

|                | 1-(2.5)=1.5                        | 0+(-1.5)=1.5      | L               | -2.5 |

|                | 1-(-2.5)=3.5                       | -1.5+(3.5)=2      | Н               | 2.5  |

|                | 1-(2.5)=1.5                        | 2+(-1.5)=0.5      | Н               | 2.5  |

Output voltages at various blocks of sigma-delta ADC

# he **Processing** es Commentional investment of the DCD

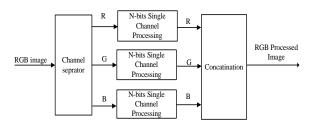

Conventional image processing takes the RGB input image and performs the required processing on the individual channels(Fig.2), or on the image as a whole (Fig.3).

3. Proposed Architecture of SDM-Based Image

Fig. 2. Conventional architecture of separated channel image processing

Fig. 3.Conventional architecture image processing as a whole

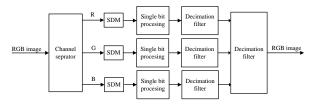

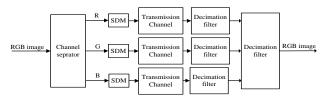

The proposed architecture for SDM-based single-bit image processing is shown in Fig.4, which depicts how the SDM technique can be applied to an RGB image. It is generally possible to apply it to any image, including grey, binary, or colored images.

For the case of RGB images, the SDM technique is applied individually on each color by separating it with the help of a separator block in MATLAB. Each eightbit color channel is then passed through SDM for converting the multi-bits to a single bit. The SDM block contains the over-sampling ratio (OSR) that causes the increase in the total number of samples as per the principle shown in equation (1).

Number of Samples=Original Samples  $\times$  OSR (1)

All the samples are then moved to a single-bit processing block for performing any image processing operation.

Since the sampling rate has been increased with the OSR ratio, applying a decimation filter at the output becomes mandatory to bring the rate to its original value.

The different channels of the processed image are then concatenated to produce the same RGB image.

In the proposed design, the dimensions of the input image are  $720 \times 720$ , where each pixel is 8-bit wide. The total bits in individual channels are  $720 \times 720 \times 8=4147200$ , and after passing through the OSR block with OSR 32, the total number of single bits would be 132710400. This single-bit can now be transmitted on the channel or easily processed with simple gates.

One of the significant constraints of the proposed design is the total number of cycles consumed. As the SDM-based approach has oversampling ratio and with increased OSR data rate increases. The increased data rate cause more processing time while with less resource consumption.

Fig. 4.Proposed architecture for SDM based single bit image processing

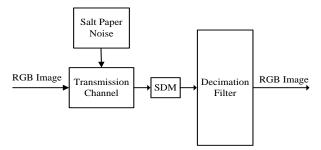

Fig. 5 shows the architecture of single-bit image transmission over the data transmission channel. As shown in Fig.4, the image is converted to three different channels before passing through the SDM block.

Fig. 5.Proposed architecture for SDM based single bit image transmission

The SDM block causes the OSR to work here and increases the total single-bit samples. The single-bit samples can then be transmitted over any communication channel by reducing the total bandwidth requirement by the factor of:

# 1/Original Data Rate (2)

To produce the impact of the channel in real-time, the salt and paper noise with a range of variance values is added, and number of simulations is carried out. The noisy image is passed to the decimation filter then to convert the single-bit SDM-based filter to back in multi-

© Mehran University of Engineering and Technology 2023

bit. The data rate increased with OSR has now been reduced to its original value.

This single-bit transmission of the image not only reduces the bandwidth but also helps in getting rid of other image-related processing, like encoding or encryption.

As the OSR causes the noise floor to be flattened and reduced, the effect may be observed in SDM-based images in increased SNR.

#### 4. MATLAB-Based Simulations and Results

An input RGB image of Innaya (Fig.6) of dimensions  $720 \times 720$  is given to the channel separator block for getting separate Red, Green, and Blue channels.

Fig. 6.The input RGB image of Innaya for single-bit transmission

To check the effect of noise supposed to be included while transmission, the prevalent salt and paper noise with different variance values is added to the image.

Fig. 7. Salt Paper noise added image

Each RGB channel is moved to the SDM block, where the OSR cause the data rate to be increased by a factor of 32. No further image compression or channel coding is applied, while at the receiver decimation filter is used to return the data rate to its original value.

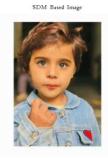

Fig. 8 shows the SDM-based single-bit image, reconstructed by applying a decimation filter and combining the separate channels to get the same RGB image.

While observing the two (Fig.7-8), it is clear that SDM brings no generic effect on the original image, and 105

the reconstructed image is the replica of the original input image. The original and SDM-based image is then compared to see the difference between the two.

A tow dimensional error matrix is generated when the reconstructed image is subtracted from the original image. The produced result is presented in Fig. 9.

Fig. 8.SDM based single bit transmitted and reconstructed image of Innaya

The advantage of oversampling in delta-sigma modulation is that the noises are spread over a more extensive frequency range, reducing the noise spectral density that in turn causes the SDM systems to be more immune to noise.

The proposed architecture was further investigated to verify the concept by looking into some performance parameters like signal-to-noise ratio, mean square error, and peak signal-to-noise ratio at a range of noise variance values.

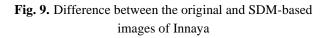

As the signal-to-noise ratio and the mean square error are inversely proportional to the noise variance, the same results are observed in simulations with a conspicuous point that due to OSR in SDM, less effect of variance is observed on SDM-based image.

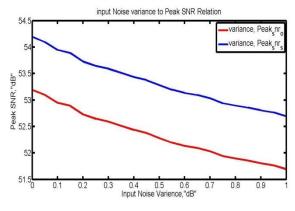

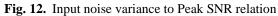

Fig. 10 shows the graph of input noise variance to SNR relation for both the input and SDM-based images. The values of both parameters are taken into dB.

Fig. 10. Input noise variance to SNR relation

It may be observed from the variance to SNR relation that in comparison to the original image, the SNR of the SDM-based image observes less effect of input noise variance, and hence in a noisy environment SDM may play a vital role.

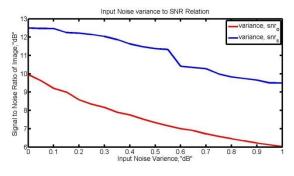

Fig. 11. Input noise variance to MSE relation

Another performance parameter considered is the mean square error. The graph in Fig.11 shows that for SDM-based images less mean square error is observed than the original input image.

The peak SNR to noise variance graph is shown in Fig.12. Like the other two parameters, the SDM-based image shows more Peak SNR value for SDM-based image resulting in the reconstruction of the degraded image even better than the original image.

#### **5.** Conclusion and Future Work

Since its exceptional use, sigma-delta modulation has diversified the digital signal processing domain by incorporating features like the oversampling ratio. With increased OSR, the SNR, Peak SNR, MSE, and other performance parameters are improved, making the overall processing much more straightforward and reducing the power requirements.

In this paper, the SDM is applied to a multi-bit RGB image for its single-bit transmission, and its various performance matrices are observed and analyzed to see if the SDM may be used in this new domain of singlebit image processing. Besides, the proposed architecture of single-bit image processing is also discussed in detail.

The various simulation results demonstrate the importance of SDM and open the doors of its use in the image processing domain, which could drastically reduce the bandwidth requirements for the transmission of digital images.

In the future, the SDM will be investigated and applied to various image processing algorithms for image filtration and enhancement, along with its hardware-based implementation on FPGAs; while it is assumed that the images are digital and in the format that an FPGA may process. Besides, the applications for SDM-based image processing would be more generic and may accept some loss of information rather than biomedical image processing or more sensitive fields.

# 6. Acknowledgement

This work is supported by the Department of Electronic Engineering of Quaid-e-Awam University of Engineering, Science and Technology Campus Larkana Pakistan.

# 7. References

- B. K. Kundu, "THz image processing and its applications", in Generation, Detection and Processing of Terahertz Signals, ed: Springer, pp. 123-137, 2022.

- [2] Y. Hou, Q. Li, C. Zhang, G. Lu, Z. Ye, Y. Chen, et al., "The state-of-the-art review on applications of intrusive sensing, image processing techniques, and machine learning methods in pavement monitoring and analysis", Engineering, vol. 7, pp. 845-856, 2021.

- [3] S. Kaur and C. Diwaker, "An image processing techniques for pattern detection in covid-19", 6th International Conference on Signal Processing, Computing and Control, pp. 728-735, 2021.

- [4] M. Adimoolam, A. John, N. Balamurugan, and T. Ananth Kumar, "Green ICT communication, networking and data processing", Green

© Mehran University of Engineering and Technology 2023

computing in smart cities: Simulation and techniques, ed: Springer, 2021, pp. 95-124.

- [5] V. Subramaniam, "Efficient image compression scheme to minimize storage and bus bandwidth requirements", ed: Google Patents, 2012.

- [6] E. C. Anderson, "Transmission bandwidth and memory requirements reduction in a portable image capture device by eliminating duplicate image transmissions", ed: Google Patents, 2007.

- Y. Rao, W. Zhao, Z. Zhu, J. Lu, and J. Zhou,

"Global filter networks for image classification", Advances in Neural Information Processing Systems, vol. 34, pp. 980-993, 2021.

- [8] S. M. Qasim, A. A. Telba, and A. Y. AlMazroo, "FPGA design and implementation of matrix multiplier architectures for image and signal processing applications", International Journal of Computer Science and Network Security, vol. 10, pp. 168-176, 2010.

- [9] A. Pathan and T. D. Memon, "An optimised 3× 3 shift and add multiplier on FPGA", in 2017 14th International Bhurban Conference on Applied Sciences and Technology (IBCAST), 2017, pp. 346-350.

- [10] A. Pathan, T. D. Memon, and S. Memon, "A carry-look ahead adder based floating-point multiplier for adaptive filter applications," International Journal of Computing and Digital Systems, vol. 7, pp. 95-102, 2018.

- [11] A. Pathan, T. D. Memon, S. Keerio, and I. H. Kalwar, "FPGA Based performance analysis of multiplier policies for FIR filter," in 2016 International Conference on Advances in Electrical, Electronic and Systems Engineering (ICAEES), 2016, pp. 17-20.

- [12] T. D. Memon and A. Pathan, "An approach to LUT based multiplier for short word length DSP systems," in 2018 International Conference on Signals and Systems (ICSigSys), 2018, pp. 276-280.

- [13] A. Pathan, T. D. Memon, F. K. Sohu, and M. A. Rajput, "Analysis of Existing and Proposed 3-Bit and Multi-Bit Multiplier Algorithms for FIR Filters and Adaptive Channel Equalizers on FPGA," Quaid-E-Awam University Research Journal of Engineering, Science & Technology, Nawabshah., vol. 19, pp. 81-89, 2021.

- [14] A. Srivastava, M. S. Gupta, and G. Kaur, "Energy efficient transmission trends towards future green cognitive radio networks (5G): Progress, taxonomy and open challenges," Journal of Network and Computer Applications, vol. 168, p. 102760, 2020.

- [15] N. Mital, E. Özyilkan, A. Garjani, and D. Gündüz, "Neural distributed image compression with cross-attention feature alignment," in Proceedings of the IEEE/CVF Winter Conference on Applications of Computer Vision, 2023, pp. 2498-2507.

- [16] H. Fu, F. Liang, J. Liang, B. Li, G. Zhang, and J. Han, "Asymmetric Learned Image Compression with Multi-Scale Residual Block, Importance Scaling, and Post-Quantization Filtering," IEEE Transactions on Circuits and Systems for Video Technology, 2023.

- S. S. Tamboli, R. Butta, T. S. Jadhav, and A. Bhatt, "Optimized active contor segmentation model for medical image compression," Biomedical Signal Processing and Control, vol. 80, p. 104244, 2023.

- [18] M. U. Lokumarambage, V. S. S. Gowrisetty, H. Rezaei, T. Sivalingam, N. Rajatheva, and A. Fernando, "Wireless end-to-end image transmission system using semantic communications," IEEE Access, 2023.

- [19] S. Tang, Q. Yang, L. Fan, X. Lei, Y. Deng, and A. Nallanathan, "Contrastive learning based semantic communication for wireless image transmission," arXiv preprint arXiv:2304.09438, 2023.

- [20] J. Wu, C. Wu, Y. Lin, T. Yoshinaga, L. Zhong, X. Chen, et al., "Semantic segmentation-based semantic communication system for image transmission", Digital Communications and Networks, 2023.

- [21] W. Zhang, Y. Wang, M. Chen, T. Luo, and D. Niyato, "Optimization of image transmission in a cooperative semantic communication networks", arXiv preprint arXiv:2301.00433, 2023.

- [22] M. Yang and H.-S. Kim, "Deep joint sourcechannel coding for wireless image transmission with adaptive rate control", IEEE International Conference on Acoustics, Speech and Signal Processing, pp. 5193-5197, 2022.

- Y. Li, X. Chen, and X. Deng, "Lightweight Deep Joint Source-Channel Coding for Gauss-Markov Sources over AWGN channel," in 2023

IEEE Wireless Communications and Networking Conference (WCNC), 2023, pp. 1-6.

- [24] G. Zhang, Q. Hu, Y. Cai, and G. Yu, "Adaptive CSI Feedback for Deep Learning-Enabled Image Transmission," arXiv preprint arXiv:2302.13477, 2023.

- [25] C. Karamanli, T.-Y. Tung, and D. Guenduez, "Model-Driven Deep Joint Source-Channel Coding over Time-Varying Channels," in WSA & SCC 2023; 26th International ITG Workshop on Smart Antennas and 13th Conference on Systems, Communications, and Coding, 2023, pp. 1-6.

- [26] N. O'Mahony, S. Campbell, A. Carvalho, S. Harapanahalli, G. V. Hernandez, L. Krpalkova, et al., "Deep learning vs. traditional computer vision," in Advances in Computer Vision: Proceedings of the 2019 Computer Vision Conference (CVC), Volume 1 1, 2020, pp. 128-144.

- [27] J. D. Reiss, "Understanding sigma-delta modulation: The solved and unsolved issues," Journal of the Audio Engineering Society, vol. 56, pp. 49-64, 2008.

- [28] A. Vlachos, N. Temenos, and P. P. Sotiriadis, "Exploring the Effectiveness of Sigma-Delta Modulators in Stochastic Computing-Based FIR Filtering," in 2021 10th International Conference on Modern Circuits and Systems Technologies, 2021, pp. 1-4.

- [29] N. Saraf, K. Bazargan, D. J. Lilja, and M. D. Riedel, "IIR filters using stochastic arithmetic", Design, Automation & Test in Europe Conference & Exhibition, pp. 1-6, 2014.

- [30] A. Chang, T. D. Memon, Z. M. Hussain, I. H. Kalwar, and B. S. Chowdhry, "Design and analysis of single-bit ternary matched filter", Wireless Personal Communications, vol. 106, pp. 1915-1929, 2019.

- [31] Y. Liu, P. M. Furth, and W. Tang, "Hardwareefficient delta sigma-based digital signal processing circuits for the internet-of-things", Journal of Low Power Electronics and Applications, vol. 5, pp. 234-256, 2015.

- [32] A. Z. Sadik, Z. M. Hussain, and P. O'Shea, "Adaptive algorithm for ternary filtering", Electronics Letters, vol. 42, pp. 420-421, 2006.

- [33] T. D. Memon, A. Pathan, and P. Beckett, "FPGA based implementation and area performance analysis of sigma-delta modulated steepest algorithm for channel equalization," in 2018 12th International conference on signal processing and communication Systems, pp. 1-6, 2018.

- [34] A. Pathan and T. D. Memon, "Sigma-delta modulation based adaptive channel equalizer based on Wiener–Hopf equations", Wireless Personal Communications, vol. 116, pp. 1123-1135, 2021.

- [35] A. Z. Sadik and Z. M. Hussain, "Short wordlength LMS filtering", 9th International symposium on signal processing and its applications, 2007, pp. 1-4, 2007.

- [36] Z. M. Hussain, "Energy-efficient systems for smart sensor communications", 30th International Telecommunication Networks and Applications Conference, pp. 1-4, 2020.

- [37] A. Pathan and T. D. Memon, "Sigma-delta modulation based single-bit adaptive DSP algorithms for efficient mobile communication", Circuits, Systems, and Signal Processing, vol. 40, pp. 1788-1801, 2021.

- [38] W. Chou, P. W. Wong, and R. M. Gray, "Multistage sigma-delta modulation", IEEE Transactions on Information theory, vol. 35, pp. 784-796, 1989.